Programming the FPGA Through JTAG¶

Both the FPGA and the AM57xx JTAG interfaces are routed to the top-side Hirose J2 connector as separate JTAG chains.

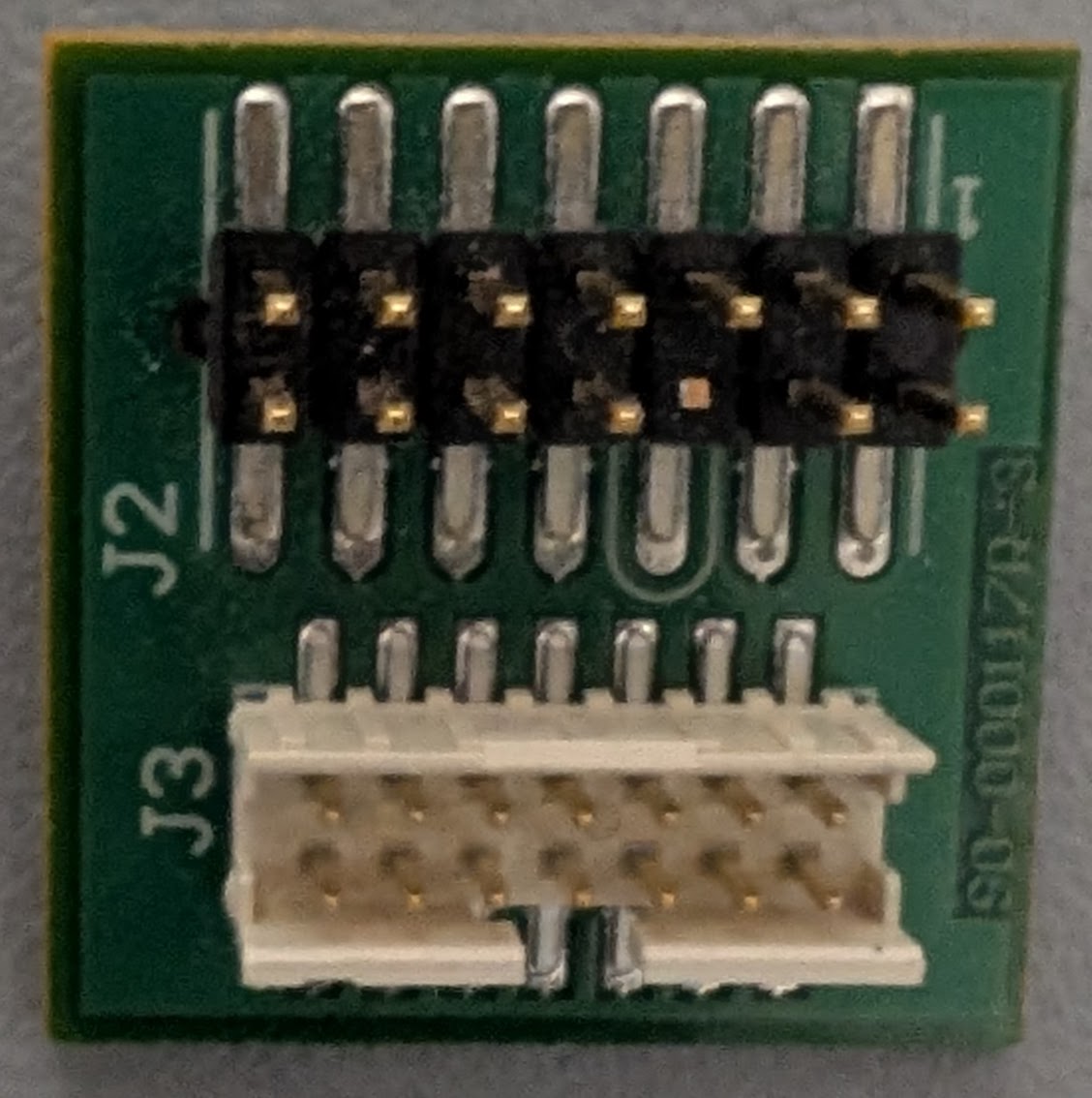

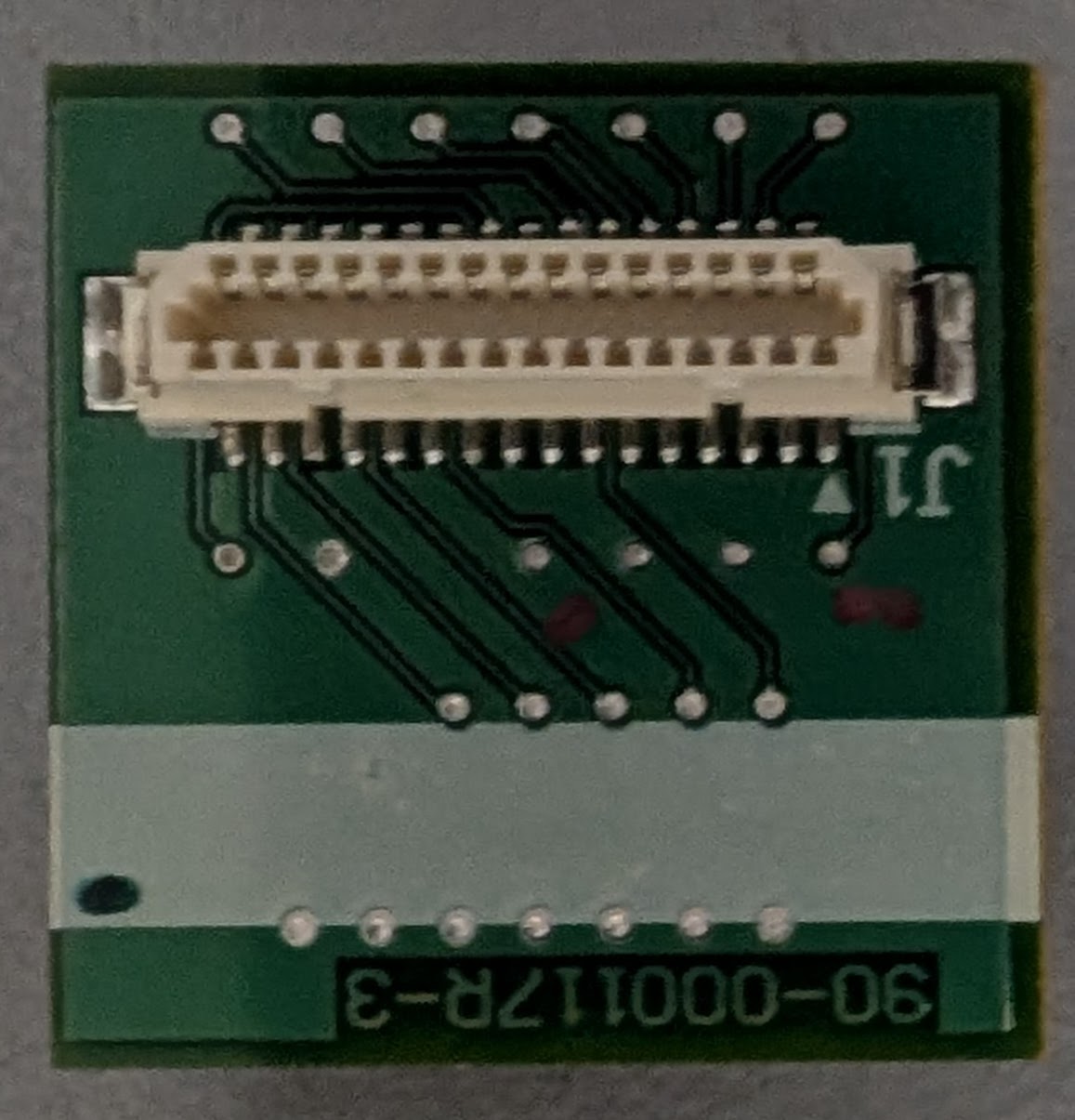

The MitySOM-AM57x Development Kits include a small break-out PCB that interfaces with the SOM J2 connector and provides a standard FPGA JTAG header compatible with standard AMD / Xilinx debug PODs as well as a second header that will work with most TI compatible JTAG PODs. Pictures of the break-out PCB are shown below.

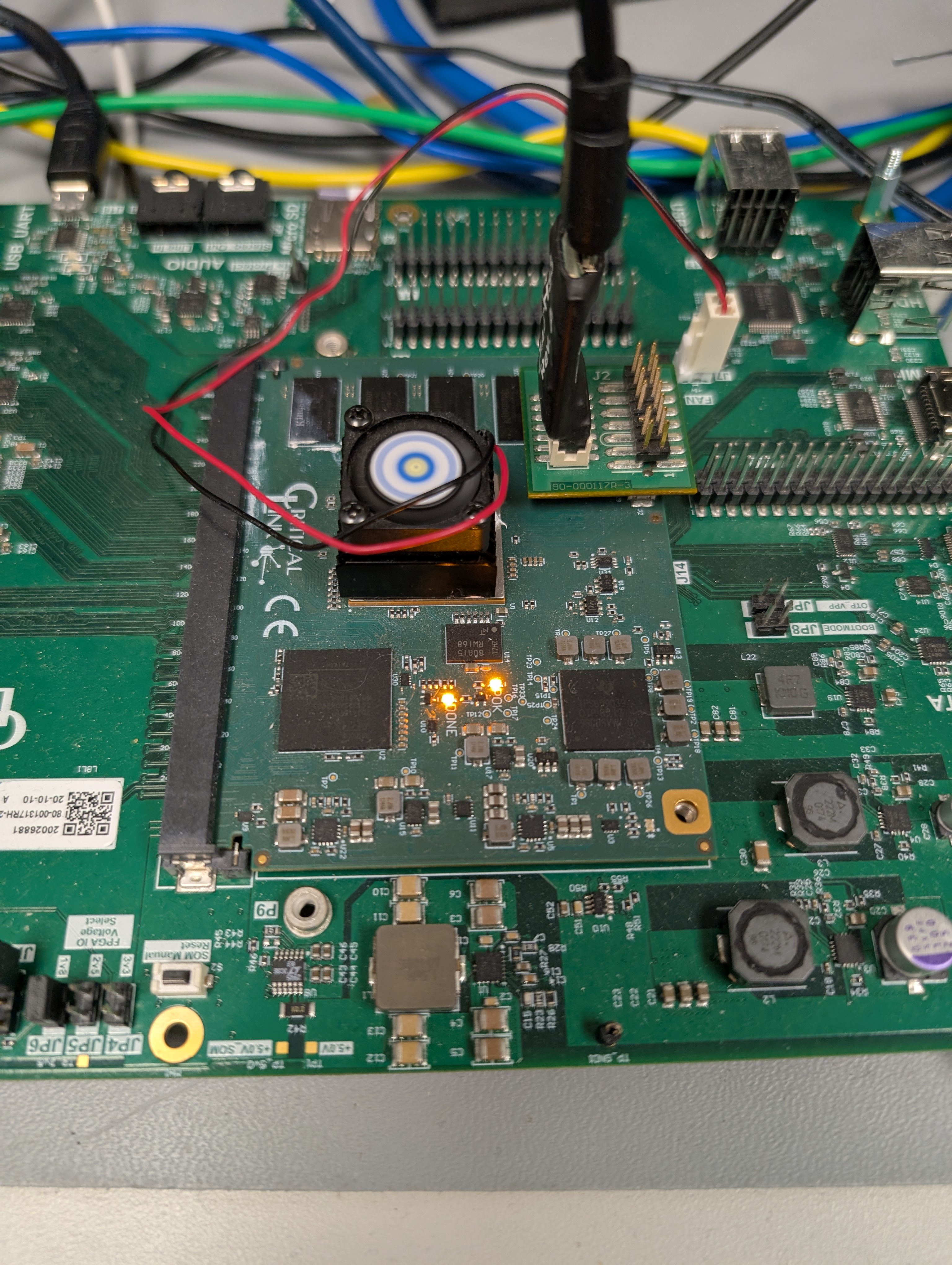

The picture below shows the board attached to a MitySOM-AM57x SOM with a Digilent USB Programming Adapter attached to the FPGA debug interface.

Critical Link recommends that you attached the adapter board and associated PODs while the modules is powered off.

Once the adapter is connected and the SOM is powered, you can program the FPGA bitstream directly using the standard Vivado programming toolchain flow.

Critical Link recommends that customers break into the uBoot command prompt and program the FPGA bitstream via JTAG prior to loading / running the linux OS kernel. This will avoid false or unhandled interrupts or driver issues with the kernel. If the FPGA is reconfigured while runnning linux, all associated FPGA drivers should be unloaded prior to reprogramming and the reloaded after the bitstream is reconfigured.

While connected, you can use standard AMD / Xilinx debugging features such as the Chipscope ILA to support developing your FPGA fabric image.

Go to top