SOM Video Input(VIP) from FPGA¶

Objective¶

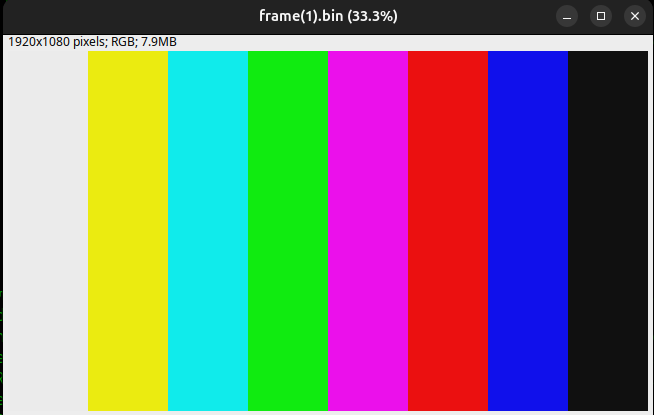

Simulate a simple RGB color bar pattern at 1920 x 1080p with 24-bit RGB and embedded SYNCs for the AM57x. This is strictly following the ITU-R BT.1120-9 spec for sync codes and line timing. The goal of this is to test and demonstrate the MitySOM-AM57x / FPGA PORT A 24-bit VIP interface.

Prerequisites¶

Reference images for this test can be found here: Repositories and Pre-built Images

The reference Micro-SD card can be used: SD Card

The reference FPGA project can be found here: FPGA Reference Design

Steps¶

- The FPGA VIP core is continuously sending a test pattern over the VIP interface after it is programmed. The following will capture a raw frame containing the 1920 x 1080p 24-bit RGB image that is a color bar test pattern.

yavta --skip 1 -c2 -fRGB24 -F -s1920x1080 /dev/video1 --file=frame.bin

NOTE The above command captures two frames and discards the first frame. Since the FPGA is continuously transmitting, the first frame may be corrupt until the FIFOs sync up. Yavta appends to the frame.bin file. It does not overwrite the file. - Copy frame.bin to host computer

scp frame.bin user@<IP_ADDRESS>:/home/user/frame.bin

- Install imagej to view the raw image

sudo apt install imagej

- Launch imagej

- Navigate to toolbar->file->Import->Raw...

- Select frame.bin

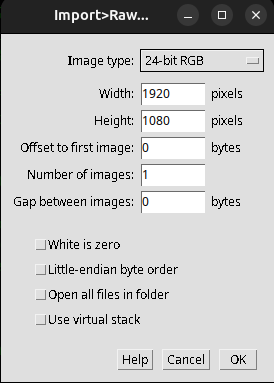

- In the popup window change the settings to the following:

- Select "OK"

- Navigate to toolbar->file->Import->Raw...

- The raw image should look like the following:

Go to top